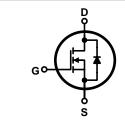

N-Channel Enhancement Mode Power Mosfet

#### **Description**

The FIR60N20AN uses advanced trench technology and design to provide excellent RDS(ON) with low gate charge. It can be used in a wide variety of applications.

#### **General Features**

- $V_{DS}$  =200V, $I_{D}$  =60A  $R_{DS(ON)}$  <32m $\Omega$  @  $V_{GS}$ =10V

- High density cell design for ultra low Rdson

- Fully characterized avalanche voltage and current

- Good stability and uniformity with high E<sub>AS</sub>

- Excellent package for good heat dissipation

- Special process technology for high ESD capability

## **Application**

- Power switching application

- Hard switched and high frequency circuits

- Uninterruptible power supply

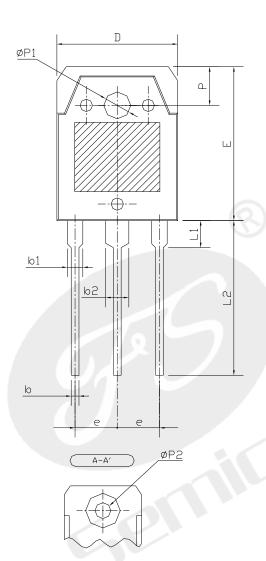

#### PIN Connection TO-3P

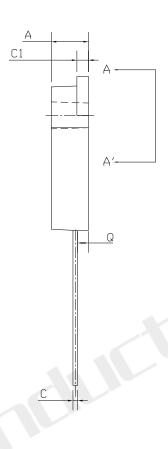

#### **Marking Diagram**

′ = Year

A = Assembly Location

WW = Work Week

FIR60N20AN = Specific Device Code

**Package Marking and Ordering Information**

| Device Marking | Device      | Device Package | Reel Size | Tape width | Quantity |

|----------------|-------------|----------------|-----------|------------|----------|

| FIR60N20AN     | FIR60N20ANG | TO-3P          | -         | -          | -        |

## Absolute Maximum Ratings (T<sub>C</sub>=25 ℃ unless otherwise noted)

| Parameter                                        | Symbol                | Limit      | Unit       |

|--------------------------------------------------|-----------------------|------------|------------|

| Drain-Source Voltage                             | V <sub>DS</sub>       | 200        | V          |

| Gate-Source Voltage                              | V <sub>G</sub> s      | ±20        | V          |

| Drain Current-Continuous                         | I <sub>D</sub>        | 60         | A          |

| Drain Current-Continuous(T <sub>C</sub> =100°C)  | I <sub>D</sub> (100℃) | 42         | Α          |

| Pulsed Drain Current                             | I <sub>DM</sub>       | 280        | Α          |

| Maximum Power Dissipation                        | P <sub>D</sub>        | 300        | W          |

| Derating factor                                  |                       | 2.0        | W/℃        |

| Single pulse avalanche energy (Note 5)           | E <sub>AS</sub>       | 506        | mJ         |

| Operating Junction and Storage Temperature Range | $T_{J}, T_{STG}$      | -55 To 175 | $^{\circ}$ |

## **Thermal Characteristic**

| Thermal Resistance, Junction-to-Case <sup>(Note 2)</sup> | $R_{	heta JC}$ | 0.5 | °C/W |

|----------------------------------------------------------|----------------|-----|------|

|----------------------------------------------------------|----------------|-----|------|

## Electrical Characteristics (T<sub>C</sub>=25°C unless otherwise noted)

| Parameter                          | Symbol              | Condition                                                            | Min | Тур  | Max  | Unit     |

|------------------------------------|---------------------|----------------------------------------------------------------------|-----|------|------|----------|

| Off Characteristics                |                     |                                                                      |     |      |      |          |

| Drain-Source Breakdown Voltage     | BV <sub>DSS</sub>   | V <sub>GS</sub> =0V I <sub>D</sub> =250μA                            | 200 | 220  | -    | V        |

| Zero Gate Voltage Drain Current    | I <sub>DSS</sub>    | V <sub>DS</sub> =200V,V <sub>GS</sub> =0V                            | -   | -    | 1    | μΑ       |

| Gate-Body Leakage Current          | I <sub>GSS</sub>    | V <sub>GS</sub> =±20V,V <sub>DS</sub> =0V                            | -   | -    | ±100 | nA       |

| On Characteristics (Note 3)        | ·                   |                                                                      |     | •    |      |          |

| Gate Threshold Voltage             | V <sub>GS(th)</sub> | V <sub>DS</sub> =V <sub>GS</sub> ,I <sub>D</sub> =250μA              | 2   | 3.2  | 4    | V        |

| Drain-Source On-State Resistance   | R <sub>DS(ON)</sub> | V <sub>GS</sub> =10V, I <sub>D</sub> =20A                            | -   | 24   | 32   | mΩ       |

| Forward Transconductance           | <b>g</b> FS         | V <sub>DS</sub> =5V,I <sub>D</sub> =30A                              | 40  | -    | -    | S        |

| Dynamic Characteristics (Note4)    |                     |                                                                      |     |      |      |          |

| Input Capacitance                  | C <sub>lss</sub>    | \/ -F0\/\/ -0\/                                                      | -   | 6200 | -    | PF       |

| Output Capacitance                 | C <sub>oss</sub>    | V <sub>DS</sub> =50V,V <sub>GS</sub> =0V,                            | -   | 950  | 4-1  | PF       |

| Reverse Transfer Capacitance       | C <sub>rss</sub>    | F=1.0MHz                                                             | -   | 460  | _    | PF       |

| Switching Characteristics (Note 4) | 12                  |                                                                      |     |      |      |          |

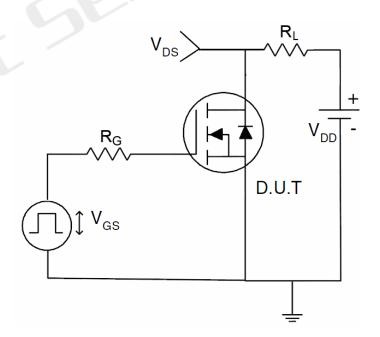

| Turn-on Delay Time                 | t <sub>d(on)</sub>  |                                                                      |     | 33   | -    | nS       |

| Turn-on Rise Time                  | t <sub>r</sub>      | V <sub>DD</sub> =100V, R <sub>L</sub> =15Ω                           | 1-/ | 20   | -    | nS       |

| Turn-Off Delay Time                | t <sub>d(off)</sub> | $V_{GS}$ =10V, $R_{G}$ =2.5 $\Omega$                                 | -   | 21   | -    | nS       |

| Turn-Off Fall Time                 | t <sub>f</sub>      |                                                                      | -   | 31   | -    | nS       |

| Total Gate Charge                  | Qg                  | V -400V I -20A                                                       | -   | 130  |      | nC       |

| Gate-Source Charge                 | Q <sub>gs</sub>     | $V_{DS}$ =100V, $I_{D}$ =30A,<br>$V_{GS}$ =10V                       | -   | 36   |      | nC       |

| Gate-Drain Charge                  | $Q_{gd}$            | V <sub>GS</sub> =10V                                                 | -   | 46   |      | nC       |

| Drain-Source Diode Characteristics |                     |                                                                      | •   |      |      |          |

| Diode Forward Voltage (Note 3)     | V <sub>SD</sub>     | V <sub>GS</sub> =0V,I <sub>S</sub> =30A                              | -   |      | 1.2  | V        |

| Diode Forward Current (Note 2)     | Is                  |                                                                      | -   | -    | 60   | Α        |

| Reverse Recovery Time              | t <sub>rr</sub>     | TJ = 25°C, IF = 30A                                                  | -   | 42   |      | nS       |

| Reverse Recovery Charge            | Qrr                 | di/dt = 100A/µs <sup>(Note3)</sup>                                   | -   | 66   |      | nC       |

| Forward Turn-On Time               | t <sub>on</sub>     | Intrinsic turn-on time is negligible (turn-on is dominated by LS+LD) |     |      |      | y LS+LD) |

## Notes:

- 1. Repetitive Rating: Pulse width limited by maximum junction temperature.

- **2.** Surface Mounted on FR4 Board,  $t \le 10$  sec.

- **3.** Pulse Test: Pulse Width ≤ 300µs, Duty Cycle ≤ 2%.

- **4.** Guaranteed by design, not subject to production

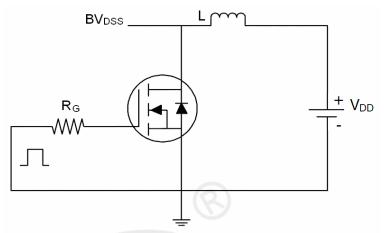

- 5. E\_{AS} condition: j=25  $^{\circ}\text{C}\,\text{,V}_{DD}\text{=}50\text{V},\text{V}_{G}\text{=}10\text{V},\text{L=}0.5\text{mH,Rg=}25\Omega$

## **Test Circuit**

# 1) E<sub>AS</sub> test Circuits

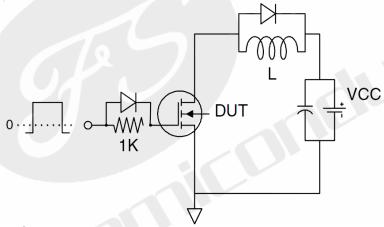

# 2) Gate charge test Circuit

# 3) Switch Time Test Circuit

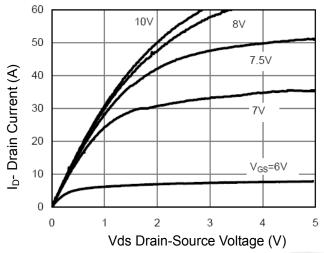

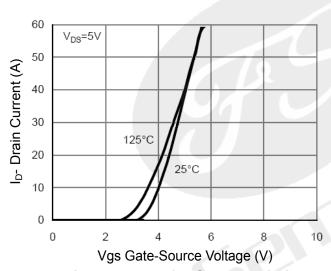

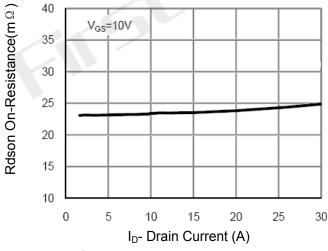

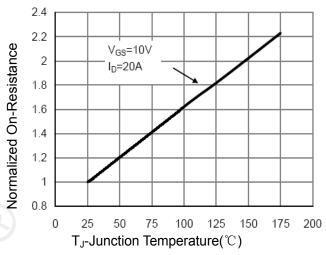

## Typical Electrical and Thermal Characteristics (Curves)

**Figure 1 Output Characteristics**

**Figure 2 Transfer Characteristics**

Figure 3 Rdson- Drain Current

**Figure 4 Rdson-Junction Temperature**

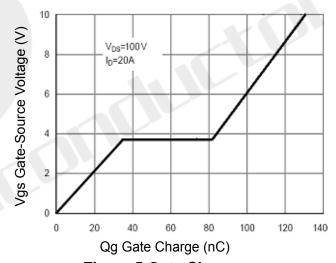

Figure 5 Gate Charge

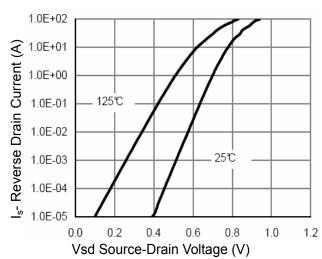

Figure 6 Source- Drain Diode Forward

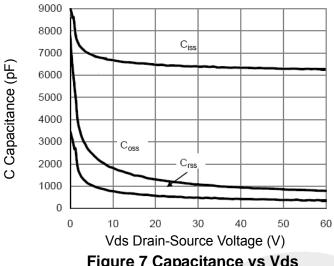

Figure 7 Capacitance vs Vds

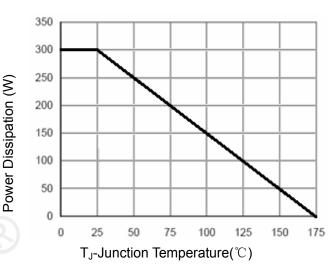

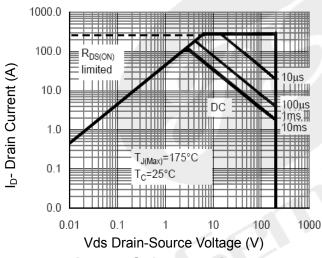

Figure 9 Power De-rating

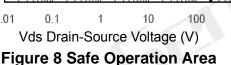

Figure 10 Current De-rating

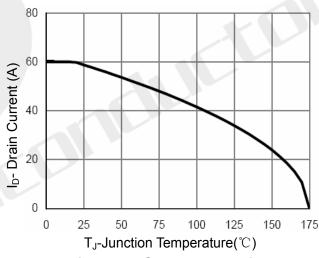

**Figure 11 Normalized Maximum Transient Thermal Impedance**

Square Wave Pluse Duration(sec)

# **Package Outline Dimensions**

| SYMBOL | MIN   | NDM    | MAX   |

|--------|-------|--------|-------|

| А      | 4.60  | 4.80   | 5.00  |

| b      | 0.80  | 1.00   | 1.20  |

| b1     | 1.80  | 2.00   | 2.20  |

| b2     | 2.80  | 3.00   | 3.20  |

| С      | 0.55  | 0.60   | 0.75  |

| C1     | 1.45  | 1.50   | 1.65  |

| D      | 15.40 | 15.60  | 15.80 |

| E      | 19.70 | 19.90  | 20.10 |

| е      | 5.15  | 5.45   | 5.75  |

| L1     | 3.30  | 3.50   | 3.70  |

| L2     | 19.80 | 20.00  | 20.20 |

| Р      | 4.80  | 5.00   | 5.20  |

| ØP1    | 3.30  | 3.40   | 3.50  |

| øP2    |       | (3.20) |       |

| Q      | 1.20  | 1.40   | 1.60  |

#### Declaration

- FIRST reserves the right to change the specifications, the same specifications of products due to different packaging line mold, the size of the appearance will be slightly different, shipped in kind, without notice!

Customers should obtain the latest version information before ordering, and verify whether the relevant information is complete and up-to-date.

- Any semiconductor product under certain conditions has the possibility of failure or failure, The buyer has the responsibility to comply with safety standards and take safety measures when using FIRST products for system design and manufacturing, To avoid To avoid potential failure risks, which may cause personal injury or property damage!

- Product promotion endless, our company will wholeheartedly provide customers with better products!

#### **ATTACHMENT**

#### **Revision History**

| Date       | REV | Description     | Page |

|------------|-----|-----------------|------|

| 2018.01.01 | 1.0 | Initial release |      |