# FIR24N60ANG

TO-3P

# FERTURES

- TYPICAL R<sub>DS</sub>(on) = 0.19Ω

- HIGH dv/dt AND AVALANCHE CAPABILITIES

- 100% AVALANCHE TESTED

- LOW INPUT CAPACITANCE AND GATE CHARGE

- LOW GATE INPUT RESISTANCE

# DESCRIPTION

This improved version of MDmesh<sup>™</sup> which is based on Multiple Drain process represents the new benchmark in high voltage MOSFETs. The resulting product exhibits even lower on-resistance, impressively high dv/dt and excellent avalanche characteristics. The adoption of the Company's proprietary strip technique yields overall performances that are significantly better than that of similar competition's products.

# APPLICATIONS

The MDmesh<sup>™</sup> family is very suitable for increasing power density of high voltage converters allowing system miniaturization and higher efficiencies.

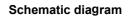

**PIN Connection**

#### **Marking Diagram**

Y A

ww

= Year = Assembly Location

= Assembly Locali

= Work Week

FIR24N60AN = Specific Device Code

| Symbol              | Parameter                                            | Value      | Unit |  |  |

|---------------------|------------------------------------------------------|------------|------|--|--|

| VDS                 | Drain-source Voltage ( $V_{GS} = 0$ )                | 600        | V    |  |  |

| V <sub>DGR</sub>    | Drain-gate Voltage ( $R_{GS} = 20 \text{ k}\Omega$ ) | 600        | V    |  |  |

| V <sub>GS</sub>     | Gate- source Voltage                                 | ±30        | V    |  |  |

| ID                  | Drain Current (continuous) at $T_C = 25^{\circ}C$    | 24         | А    |  |  |

| I <sub>D</sub>      | Drain Current (continuous) at T <sub>C</sub> = 100°C | 12.6       |      |  |  |

| I <sub>DM</sub> (•) | Drain Current (pulsed)                               | 80         |      |  |  |

| P <sub>TOT</sub>    | Total Dissipation at $T_C = 25^{\circ}C$             | 192        | W    |  |  |

| dv/dt(1)            | Peak Diode Recovery voltage slope                    | 15         | V/ns |  |  |

| V <sub>ISO</sub>    | Insulation Winthstand Voltage (DC)                   | 2500       | V    |  |  |

| T <sub>stg</sub>    | Storage Temperature                                  | -65 to 150 | °C   |  |  |

| Тj                  | Max. Operating Junction Temperature                  | 150        | °C   |  |  |

(•) Pulse width limited by safe operating area;

(1)  $I_{SD} \leq 24A$ , di/dt  $\leq 400A/\mu s$ ,  $V_{DD} \leq V_{(BR)DSS}$ ,  $T_j \leq T_{JMAX}$ .

(\*)Limited only by maximum temperature allowed

# FIR24N60ANG

#### THERMAL DATA

| Symbol    | Parameter                                         |    | Value | Unit |

|-----------|---------------------------------------------------|----|-------|------|

| Rthj-case | Thermal Resistance Junction-case M                | ax | 0.65  | W/°C |

| Rthj-amb  | Thermal Resistance Junction-ambient M             | ax | 62.5  | °C/W |

| ΤI        | Maximum Lead Temperature For Soldering<br>Purpose |    | 300   | °C   |

## **AVALANCHE CHARACTERISTICS**

| Symbol          | Parameter                                                                                               | Max Value | Unit |

|-----------------|---------------------------------------------------------------------------------------------------------|-----------|------|

| I <sub>AR</sub> | Avalanche Current, Repetitive or Not-Repetitive (pulse width limited by $T_j$ max)                      | 12        | A    |

| E <sub>AS</sub> | Single Pulse Avalanche Energy<br>(starting $T_j = 25 \text{ °C}, I_D = I_{AR}, V_{DD} = 50 \text{ V}$ ) | 650       | mJ   |

# **ELECTRICAL CHARACTERISTICS** (T<sub>CASE</sub> = 25 °C UNLESS OTHERWISE SPECIFIED) ON/OFF

| Symbol              | Parameter                                                | Test Conditions                                                         | Min. | Тур. | Max.    | Unit     |

|---------------------|----------------------------------------------------------|-------------------------------------------------------------------------|------|------|---------|----------|

| V(BR)DSS            | Drain-source<br>Breakdown Voltage                        | $I_D = 250 \ \mu A, V_{GS} = 0$                                         | 600  |      |         | V        |

| I <sub>DSS</sub>    | Zero Gate Voltage<br>Drain Current (V <sub>GS</sub> = 0) | $V_{DS}$ = Max Rating<br>$V_{DS}$ = Max Rating, T <sub>C</sub> = 125 °C |      |      | 1<br>10 | μΑ<br>μΑ |

| I <sub>GSS</sub>    | Gate-body Leakage<br>Current (V <sub>DS</sub> = 0)       | V <sub>GS</sub> = ±30 V                                                 |      |      | ±100    | nA       |

| V <sub>GS(th)</sub> | Gate Threshold Voltage                                   | $V_{DS} = V_{GS}$ , $I_D = 250 \ \mu A$                                 | 3    | 4    | 5       | V        |

| R <sub>DS(on)</sub> | Static Drain-source On<br>Resistance                     | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 12 A                           |      | 0.19 | 0.25    | Ω        |

|                     |                                                          |                                                                         |      |      |         |          |

#### ELECTRICAL CHARACTERISTICS (CONTINUE) DYNAMIC

| Symbol                                                   | Parameter Test Conditions                                                  |                                                                      | Min. | Тур.              | Max. | Unit           |

|----------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------|------|-------------------|------|----------------|

| g <sub>fs</sub> (1)                                      | Forward Transconductance                                                   | $V_{DS} > I_{D(on)} \times R_{DS(on)max,}$<br>$I_{D} = 12 \text{ A}$ |      | TBD               |      | S              |

| C <sub>iss</sub><br>C <sub>oss</sub><br>C <sub>rss</sub> | Input Capacitance<br>Output Capacitance<br>Reverse Transfer<br>Capacitance | V <sub>DS</sub> = 25V, f = 1 MHz, V <sub>GS</sub> = 0                |      | 1590<br>803<br>52 |      | pF<br>pF<br>pF |

| C <sub>oss eq.</sub> (2)                                 | Equivalent Output<br>Capacitance                                           | $V_{GS} = 0V$ , $V_{DS} = 0V$ to 400V                                |      | 130               |      | pF             |

| Rg                                                       | Gate Input Resistance                                                      | f=1 MHz Gate DC Bias=0<br>Test Signal Level=20mV<br>Open Drain       |      | 1.6               |      | Ω              |

(1) Pulsed: Pulse duration = 300  $\mu$ s, duty cycle 1.5 %.

(\*) Coss eq. is defined as a constant equivalent capacitance giving the same charging time as Coss when VDS increases from 0 to 80% VDSS.

#### SWITCHING ON

| Symbol                                               | Parameter                                                    | Test Conditions                                                                                                                             | Min. | Тур.           | Max. | Unit           |  |

|------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|----------------|------|----------------|--|

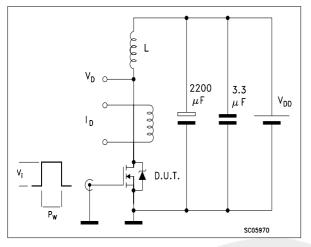

| t <sub>d(on)</sub><br>t <sub>r</sub>                 | Turn-on Delay Time<br>Rise Time                              | $V_{DD} = 200 \text{ V}, \text{ I}_{D} = 12 \text{ A}$<br>$R_{G} = 4.7\Omega \text{ V}_{GS} = 10 \text{ V}$<br>(see test circuit, Figure 3) |      | 25<br>20       | -    | ns<br>ns       |  |

| Q <sub>g</sub><br>Q <sub>gs</sub><br>Q <sub>gd</sub> | Total Gate Charge<br>Gate-Source Charge<br>Gate-Drain Charge | $V_{DD} = 400 \text{ V}, I_D = 24 \text{ A}, V_{GS} = 10 \text{ V}$                                                                         |      | 40<br>11<br>25 | 71   | nC<br>nC<br>nC |  |

#### SWITCHING OFF

| Symbol               | Parameter Test Conditions |                                                                     | Min. | Тур. | Max. | Unit |

|----------------------|---------------------------|---------------------------------------------------------------------|------|------|------|------|

| t <sub>r(Voff)</sub> | Off-voltage Rise Time     | $V_{DD} = 480 \text{ V}, \text{ I}_{D} = 24 \text{ A},$             |      | 13   |      | ns   |

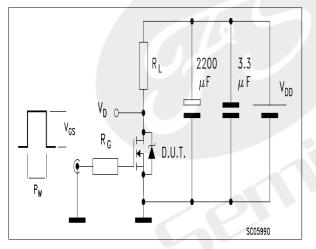

| t <sub>f</sub>       | Fall Time                 | $R_G = 4.7\Omega$ , $V_{GS} = 10 V$<br>(see test circuit, Figure 5) |      | 15   |      | ns   |

| t <sub>c</sub>       | Cross-over Time           | (                                                                   |      | 26   |      | ns   |

#### SOURCE DRAIN DIODE

| Symbol                                                 | Parameter                                                                    | Test Conditions                                                                                                             | Min. | Тур.             | Max. | Unit          |

|--------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|------------------|------|---------------|

| I <sub>SD</sub>                                        | Source-drain Current                                                         |                                                                                                                             |      |                  | 20   | А             |

| I <sub>SDM</sub> (2)                                   | Source-drain Current (pulsed)                                                |                                                                                                                             |      |                  | 80   | А             |

| V <sub>SD</sub> (1)                                    | Forward On Voltage                                                           | I <sub>SD</sub> = 24 A, V <sub>GS</sub> = 0                                                                                 |      |                  | 1.5  | V             |

| t <sub>rr</sub><br>Q <sub>rr</sub><br>I <sub>rrm</sub> | Reverse Recovery Time<br>Reverse Recovery Charge<br>Reverse Recovery Current | $I_{SD} = 24A, di/dt = 100A/$ <b>şı</b> ,<br>V <sub>DD</sub> = 100 V, T <sub>j</sub> = 25°C<br>(see test circuit, Figure 5) |      | 416<br>5.6<br>27 |      | ns<br>µC<br>A |

| t <sub>rr</sub><br>Q <sub>rr</sub><br>I <sub>rrm</sub> | Reverse Recovery Time<br>Reverse Recovery Charge<br>Reverse Recovery Current | $I_{SD}$ =24A,di/dt=100A/ <b>ş</b> ı<br>V <sub>DD</sub> = 100 V, T <sub>j</sub> = 150°C<br>(see test circuit, Figure 5)     |      | 544<br>7.3<br>28 |      | ns<br>µC<br>A |

Note: 1. Pulsed: Pulse duration = 300 μs, duty cycle 1.5 %.2. Pulse width limited by safe operating area.

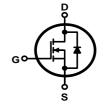

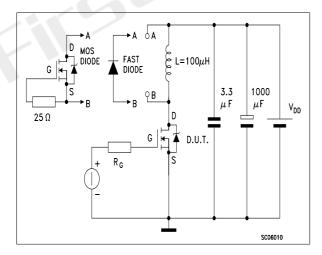

Fig. 1: Unclamped Inductive Load Test Circuit

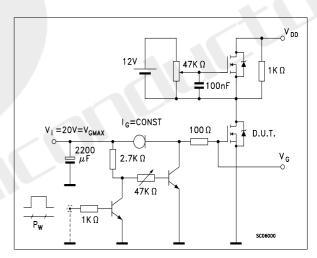

**Fig. 3:** Switching Times Test Circuit For Resistive Load

**Fig. 5:** Test Circuit For Inductive Load Switching And Diode Recovery Times

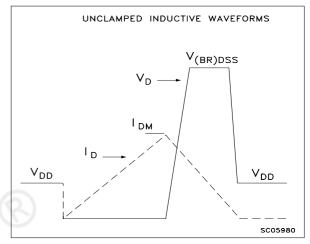

### Fig. 2: Unclamped Inductive Waveform

## Fig. 4: Gate Charge test Circuit

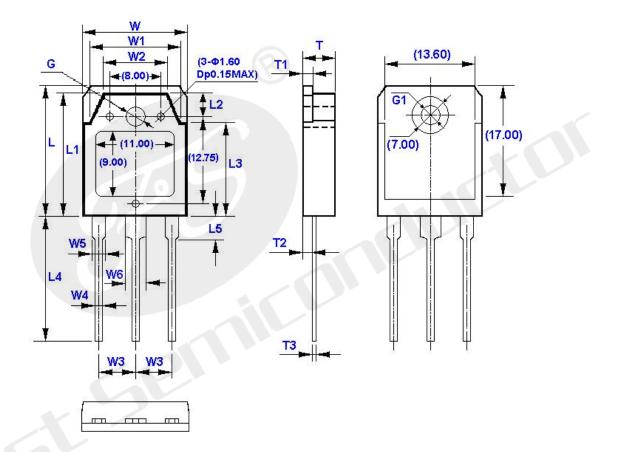

# **Package Outline Dimensions**

TO-3P

Units: mm

| 符号 — | 尺寸    |       | ·符号  | 尺寸    |       | 符号 | 尺     | 4     | 符号            | 尺    | 4    |

|------|-------|-------|------|-------|-------|----|-------|-------|---------------|------|------|

|      | Min   | Max   | 11 5 | Min   | Max   |    | Min   | Max   | 11 7          | Min  | Max  |

| W    | 15.40 | 15.80 | W5   | 1.80  | 2.20  | L3 | 13.70 | 14.10 | T2            | 1.20 | 1.60 |

| W1   | 13.40 | 13.80 | W6   | 2.80  | 3.20  | L4 | 19.70 | 20.30 | T3            | 0.55 | 0.75 |

| W2   | 9.40  | 9.80  | L    | 19.70 | 20.10 | L5 | 3.30  | 3.70  | G (Φ)<br>(正面) | 3.30 | 3.50 |

| W3   | 5.45  | (TYP) | L1   | 18.50 | 18.90 | Т  | 4.60  | 5.00  | G1(Φ)<br>(背面) | 3.10 | 3.30 |

| W4   | 0.80  | 1.20  | L2   | 3.60  | 4.00  | T1 | 1.45  | 1.65  |               |      |      |

Declaration

- FIRST reserves the right to change the specifications, the same specifications of products due to different packaging line mold, the size of the appearance will be slightly different, shipped in kind, without notice! Customers should obtain the latest version information before ordering, and verify whether the relevant information is complete and up-to-date.

- Any semiconductor product under certain conditions has the possibility of failure or failure, The buyer has the responsibility to comply with safety standards and take safety measures when using FIRST products for system design and manufacturing, To avoid To avoid potential failure risks, which may cause personal injury or property damage!

- Product promotion endless, our company will wholeheartedly provide customers with better products

#### ATTACHMENT

#### **Revision History**

| Date       | REV | Description     | Page |

|------------|-----|-----------------|------|

| 2018.01.01 | 1.0 | Initial release |      |

|            |     |                 |      |