时钟芯片 DS1302 涓流充电时钟IC DS1302Z使用说明

时钟芯片 DS1302的描述:

DS1302 可慢速充电实时时钟芯片包含实时时钟/日历和 31 字节的非易失性静态 RAM。它经过一个简单的串行接口与微处理器通信。实时时钟/日历可对秒,分,时,日,周,月,和年进行计数,对于小于31 天的月,月末的日期自动进行调整,还具有闰年校正的功能。时钟可以采用 24 小时格式或带 AM(上午)/PM(下午)的 12 小时格式。31 字节的 RAM 可以用来临时保存一些重要数据。使用同步串行通信,简化了 DS1302 与微处理器的通信。与时钟/RAM 通信仅需 3 根线:(1)RST(复位),(2)I/O(数据线)和(3)SCLK(串行时钟)。数据可以以每次一个字节的单字节形式或多达 31 字节的多字节形式传输。DS1302能在非常低的功耗下工作,消耗小于 1µW 的功率便能保存数据和时钟信息。

时钟芯片 DS1302的特点:

可对秒,分,时,日,周,月以及带闰年补偿的年进行计数

用于高速数据暂存的31字节非易失性RAM

宽工作电源电压范围:2~5.5V

2.5V时耗电小于300nA

用于时钟或RAM数据读/写的单字节或多字节数据传送方式

简单的3线接口与单片机通信

TTL兼容(VCC=5V)

可选的工业温度范围-40℃至+85℃

封装形式:DIP8和SOP8

时钟芯片 DS1302的应用领域:

使用说明:

串行时钟芯片的主要组成部分示于图 1:移位寄存器控制逻辑,振荡器,实时时钟以及 RAM。

工作原理:如图所示,RST 信号有效后,移位寄存器单元会在 SCLK 同步脉冲信号的控制下从 I/O 上串行接收 8 位指令字节,然后将 8 位指令字节进行串并转换并送至 ROM 指令译码单元。由 ROM 指令译码单元对 8 位指令字节进行译码,以决定内部寄存器的地址以及读写状态。然后在接下来的 SCLK 同步脉冲信号的控制下将 8 位数据写进或者读出相应的寄存器。数据传送也可以采用多字节方式,先将 8 位相应的指令字节写入,然后在连续的 SCLK 的脉冲信号同步下,将数据字节连续写入或读出日历/时钟寄存器(或者RAM 单元)。SCLK 脉冲的个数在单字节方式下为 8 加 8,在多字节方式下为 8 加最大可达到 248 的数。

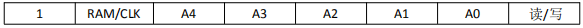

1、命令字节

命令字节示于图 2:每一数据传送由命令字节初始化,最高有效位 MSB(位 7)必须为逻辑 1。如果它是零,禁止写 DS1302。位 6 为逻辑 0 指定时钟/日历数据。逻辑 1 指定 RAM 数据。位 1 至 5 指定进行输入或输出的特定寄存器。最低有效位 LSB(位 0)为逻辑 0 指定进行写操作(输入);逻辑 1 指定进行读操作(输出)。命令字节总是从最低有效 LSB 位 0 开始输入。

图2 地址/命令字节

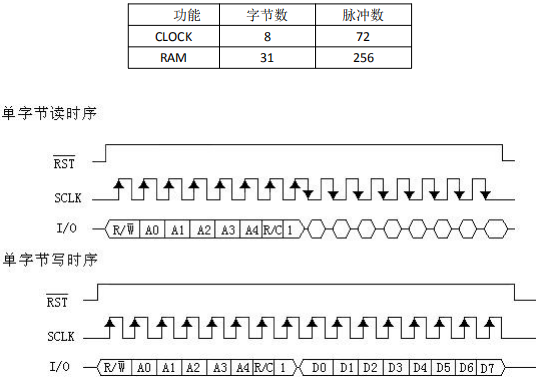

2、复位和时钟控制

通过把 RST 输入驱动至高电平来启动所有的数据传送。RST 输入有两种功能。首先,RST 接通控制逻辑,允许地址命令序列送入移位寄存器。其次,RST 可以中止数据传送。数据输入时,在时钟的上升沿数据必须有效,而数据位在时钟的下降沿输出。如果 RST 输入为低电平,那么所有的数据传送中止,且 I/O引脚变为高阻。数据传送在图 3 中说明。上电时,在 VCC 大于或等于 2.5V 之前,RST 必须为逻辑 0,此外,当把 RST 驱动至逻辑 1 的状态时,SCLK 必须为逻辑 0。

3、数据输入

跟随在输入写命令字节的 8 个 SCLK 周期之后,在下 8 个 SCLK 周期的上升沿输入数据。如果有额外的SCLK 周期,它们将被忽略。输入从位 0 开始。

4、数据输出

跟随在输入读命令字节的 8 个 SCLK 周期之后,在随后的 8 个 SCLK 周期的下降沿输出数据字节。注意,被传送的每一个数据位发生在读命令字节的最后一位之后的第一个下降沿。只要 RST 保持为高电平,如果有额外的 SCLK 周期,它们将重新发送数据字节。这一操作使之具有连续的多字节方式的读能力。另外,在 SCLK 的每一个上升沿,I/O 引脚为三态。数据从位 0 开始输出。

5、多字节方式

通过对 31(十进制)位地址寻址(地址/命令位于 1 至 5=逻辑 1),可以把时钟/日历或 RAM 寄存器规定为多字节方式。如前所述,位 6 规定时钟或 RAM 而位 0 规定读或写。在时钟\日历寄存器中的地址 9 至 31或 RAM 寄存器中的地址 31 不能存储数据。在多字节方式中读或写从地址 0 的位 0 开始。当以多字节方式写时钟寄存器时,必须按数据传送的次序写最先 8 个寄存器。但是,当以多字节方式写 RAM 时,为了传送数据不必写所有 31 个字节。不管是否写了全部 31 个字节,所写的每一个字节都将传送至 RAM。

图3 数据传送概要

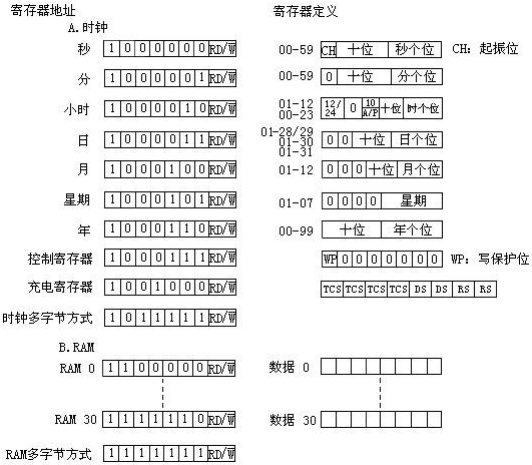

6、时钟/日历

如图 4 所示,时钟/日历包含在 7 个写/读寄存器内。包含在时钟/日历寄存器内的数据是二-十进制(BCD)码。

7、时钟暂停

秒寄存器的位 7 定义为时钟暂停位。当此位设置为逻辑 1 时,时钟振荡器停止,DS1302 被置入低功率的备份方式,其电源消耗小于 100 纳安(nanoamp)。当把此位写成逻辑 0 时,时钟将启动。

8、AM-PM/12-24 方式

小时寄存器的位 7 定义为 12 或 24 小时方式选择位。当它为高电平时,选择 12 小时方式,在 12 小时方式下,位 5 是 AM/PM 位,此位为逻辑高电平表示 PM。在 24 小时方式下,位 5 是第 2 个 10 小时位(20-23时)。

9、写保护寄存器

写保护寄存器的位 7 是写保护位。开始 7 位(位 0-6)置为零,在读操作时总是读出零。在对时钟或RAM 进行写操作之前,位 7 必须为零。当它为高电平时,写保护位禁止对任何其它寄存器进行写操作。

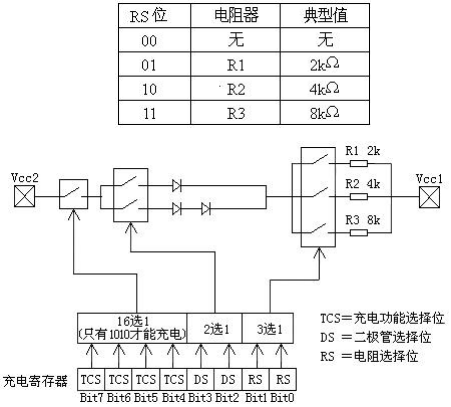

10、慢速充电(Trickle charge)寄存器

这个寄存器控制 DS1302 的慢速充电特性。图 4 的简化电路表示慢速充电器的基本组成。慢速充电选择(TCS)位(位 4-7)控制慢速充电器的选择。为了防止偶然的因素使之工作,只有 1010 模式才能使慢速充电器工作,所有其它的模式将禁止慢速充电器。DS1302 上电时,慢速充电器被禁止。二极管选择(DS)位(位 2-3)选择是一个二极管还是两个二极管连接在 Vcc2 与 Vcc1 之间。如果 DS 为 01,那么选择一个二极管;如果 DS 为 10,则选择两个二极管。如果 DS 为 00 或 11,那么充电器被禁止,与 TCS 无关。RS 位(位0-1)选择连接在 Vcc2 与 Vcc1 之间的电阻。电阻选择(RS)位选择的电阻如下:

图4 DS1302可编程慢速充电器

如果 RS 为 00,充电器被禁止,与 TCS 无关。

二极管和电阻的选择用户根据电池和超容量电容充电所需的最大电流决定。最大充电电流可以如下列所说明的那样进行计算。假定 5V 系统电源加到 Vcc2 而超容量电容接至 Vcc1。再假设慢速充电器工作时在Vcc2 和 Vcc1 之间接有一个二极管和电阻 R1。因而最大电流可计算如下:

Imax =(5.0V-二极管压降)/R1

=(5.0V-0.7V)/2kΩ

= 2.2mA

显而易见,当超容量电容充电时,Vcc2 和 Vcc1 之间的电压减少,因而充电电流将会减小。

11、时钟/日历多字节(Burst)方式

时钟/日历命令字节可规定多字节工作方式。在此方式下,最先 8 个时钟/日历寄存器可以从地址 0 的第 0 位开始连续地读或写(见图 4)。

当指定写时钟/日历的多字节方式时,如果写保护位设置为高电平,那么没有数据会传到 8 个时钟/日历寄存器(包括控制寄存器)中的任一个。在多字节方式下,慢速充电器时不可访问的。

12、RAM

静态 RAM 是 RAM 地址空间中顺序寻址的 31×8 字节。

13、RAM 多字节方式

RAM 命令字节可规定多字节工作方式。在此方式下,可以从地址 0 的第 0 位开始顺序读或写 31 字节RAM 寄存器(见图 5)。

14、寄存器概要

寄存器数据格式概要示于图 5.

图5 寄存器地址/定义

15、晶振选择

32.768kHz 的晶振可通过引脚 2 和 3(X1 和 X2)直接连接至 DS1302。所选晶振规定的负载电容量(CL)应当为 6pF。

16、电源控制

Vcc1 在单电源与电池供电的系统中提供低电源并提供低功率的电池备份。

Vcc2 在双电源系统中提供主电源,此时 Vcc1 连接到备份电源,以便在没有主电源的情况下能保存时间信息以及数据。

DS1302 由 Vcc1 或 Vcc2 两者中较大者供电。当 Vcc2 大于 Vcc1+0.2V 时,DS1302 由 Vcc2 供电。当 Vcc2+0.2V小于 Vcc1 时,DS1302 由 Vcc1 供电。

声明:本网站原创内容,如需转载,请注明出处;本网站转载的内容(文章、图片、视频)等资料版权归原网站所有。如我们采用了您不宜公开的文章或图片,未能及时和您确认,避免给双方造成不必要的经济损失,请电邮联系我们,以便迅速采取适当处理措施;邮箱:limeijun@yushin88.com